## SFF specifications are available at http://www.snia.org/sff/specifications or ftp://ftp.seagate.com/sff

#### This specification was developed by the SFF Committee prior to it becoming the SFF TA (Technology Affiliate) TWG (Technical Working Group) of SNIA (Storage Networking Industry Association).

The information below should be used instead of the equivalent herein.

POINTS OF CONTACT:

Chairman SFF TA TWG Email: SFF-Chair@snia.org

If you are interested in participating in the activities of the SFF TWG, the membership application can be found at: http://www.snia.org/sff/join

The complete list of SFF Specifications which have been completed or are currently being worked on can be found at: http://www.snia.org/sff/specifications/SFF-8000.TXT

The operations which complement the SNIA's TWG Policies & Procedures to guide the SFF TWG can be found at: http://www.snia.org/sff/specifications/SFF-8032.PDF

Suggestions for improvement of this specification will be welcome, they should be submitted to:

http://www.snia.org/feedback

SFF Committee documentation may be purchased in electronic form. SFF specifications are available at ftp://ftp.seagate.com/sff

SFF Committee

#### SFF-8418

Specification for

#### SFP+ 10 Gb/s Electrical Interface

Rev 1.4 July 30, 2015

Secretariat: SFF Committee

Abstract: This specification defines the high speed electrical interface specifications for 10 Gb/s SFP+ modules and hosts. The 8.5 Gb/s high speed electrical interface specifications are defined in FC-PI-4. The modules may optionally support lower signaling rates as well. The modules may be used to implement single-mode or multimode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm. The SFP+ module design may use one of several different optical connectors.

This specification provides a common reference for systems manufacturers, system integrators, and suppliers. This is an internal working specification of the SFF Committee, an industry ad hoc group.

This specification is made available for public review, and written comments are solicited from readers. Comments received by the members will be considered for inclusion in future revisions of this specification.

Support: This specification is supported by the identified member companies of the SFF Committee.

POINTS OF CONTACT:

Chairman SFF Committee I. Dal Allan ENDL 14426 Black Walnut Court Saratoga CA 95070 408-867-6630 endlcom@acm.org

#### EXPRESSION OF SUPPORT BY MANUFACTURERS

The following member companies of the SFF Committee voted in favor of this industry specification:

AmphenolJDS UniphaseAristaMolexBroadcomQLogicFinisarShinning ElectronicsGLGnet ElectronicsSichuanHewlett PackardSumitomoHGSTTE Connectivity

The following member companies of the SFF Committee voted against this industry specification.

Mellanox

The following member companies of the SFF Committee voted to abstain on this industry specification.

| Avago   | Fujitsu Technology GME | 3H |

|---------|------------------------|----|

| EMC     | Genesis Tech           |    |

| FCI     | Seagate                |    |

| Foxconn |                        |    |

The user's attention is called to the possibility that implementation to this Specification may require use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith. Members of the SFF Committee which advise that a patent exists are required to provide a statement of willingness to grant a license under these rights on reasonable and non-discriminatory terms and conditions to applicants desiring to obtain such a license.

#### Change History:

Rev 1.0 March 31, 2015 - Content derived from SFF-8431 Rev 4.2 excepting Sections 2.1-2.7 and 4 - Updated with current template, with exception that Table and Figure numbering is sequential and not within Section. - Converted symbols to text and editorial corrections made to case, consistency of expression, etc. - Adopted 10<sup>^</sup> for consistent expression of powers (BER et al) - Corrected references to SFF-8083 to be SFF-8071 Rev 1.1 May 8, 2015 - Added cross-references to SFF-8431 sections/tables/figures Rev 1.2 June 2, 2015 - Corrected reference to SFF-8071 in C.1.2 to be SFF-8084 - Minor editorial changes as requested Rev 1.3 June 11, 2015 - Transferred power supply Section 2 and Appendix D.17 to SFF-8419 Rev 1.4 July 30, 2015 - Updated 1.1.1 Industry Documents - Corrected Table 1 reference to low speed test method to SFF-8419 - Corrected invalid symbol conversions on p36 and p56

#### Foreword

The development work on this specification was done by the SFF Committee, an industry group. The membership of the committee since its formation in August 1990 has included a mix of companies which are leaders across the industry.

When 2 1/2" diameter disk drives were introduced, there was no commonality on external dimensions e.g. physical size, mounting locations, connector type, connector location, between vendors.

The first use of these disk drives was in specific applications such as laptop portable computers and system integrators worked individually with vendors to develop the packaging. The result was wide diversity, and incompatibility.

The problems faced by integrators, device suppliers, and component suppliers led to the formation of the SFF Committee as an industry ad hoc group to address the marketing and engineering considerations of the emerging new technology.

During the development of the form factor definitions, other activities were suggested because participants in the SFF Committee faced more problems than the physical form factors of disk drives. In November 1992, the charter was expanded to address any issues of general interest and concern to the storage industry. The SFF Committee became a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

Those companies which have agreed to support a specification are identified in the first pages of each SFF Specification. Industry consensus is not an essential requirement to publish an SFF Specification because it is recognized that in an emerging product area, there is room for more than one approach. By making the documentation on competing proposals available, an integrator can examine the alternatives available and select the product that is felt to be most suitable.

SFF Committee meetings are held during T10 weeks (see www.t10.org), and Specific Subject Working Groups are held at the convenience of the participants. Material presented at SFF Committee meetings becomes public domain, and there are no restrictions on the open mailing of material presented at committee meetings.

Most of the specifications developed by the SFF Committee have either been incorporated into standards or adopted as standards by EIA (Electronic Industries Association), ANSI (American National Standards Institute) and IEC (International Electrotechnical Commission).

If you are interested in participating or wish to follow the activities of the SFF Committee, the signup for membership and/or documentation can be found at: www.sffcommittee.com/ie/join.html

The complete list of SFF Specifications which have been completed or are currently being worked on by the SFF Committee can be found at: ftp://ftp.seagate.com/sff/SFF-8000.TXT

If you wish to know more about the SFF Committee, the principles which guide the activities can be found at: ftp://ftp.seagate.com/sff/SFF-8032.TXT

Suggestions for improvement of this specification will be welcome. They should be sent to the SFF Committee, 14426 Black Walnut Ct, Saratoga, CA 95070.

| Cross Reference of Sections, Figures and Tables                                  | 8431   | Section   |

|----------------------------------------------------------------------------------|--------|-----------|

| Industry Documents                                                               |        | 1.1.1     |

| The SFP+ Supported Standards                                                     | 1.2    | 1.2       |

| SFI Typical PCB Reach (Informative)                                              | 1.3    | 1.3       |

| Low Speed Electrical and Power Specifications                                    | 2      | 2         |

| High Speed Electrical Specification SFI                                          | 3      | 3         |

| SFI Channel Recommendation (Informative)                                         | Α.     | Α.        |

| SFI ASIC/SerDes Specification (Informative)                                      | Β.     | Β.        |

| Application Reference Boards (Normative)                                         | С.     | С.        |

| Test Methodology and Measurement (Normative)                                     | D.     | D.        |

| SFP+ Direct Attach Cable Specifications "10GSFP+Cu" (Optional)                   | Ε.     | Ε.        |

| 1.25 GBd Operation Support (Optional)                                            | F.     | F.        |

| Matlab Code for TWDP                                                             | G.     | G.        |

|                                                                                  | Figure |           |

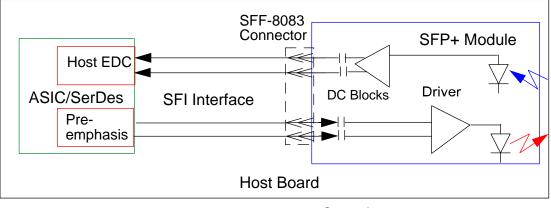

| SFI Application Reference Model                                                  | 12     | Figure 1  |

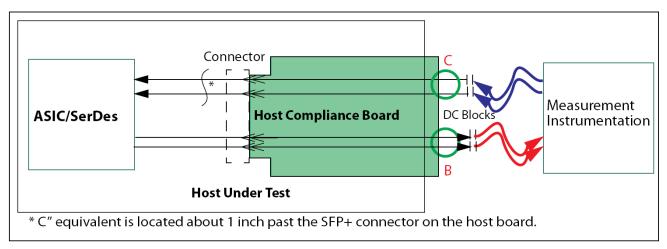

| Host Compliance Board                                                            | 13     | Figure 2  |

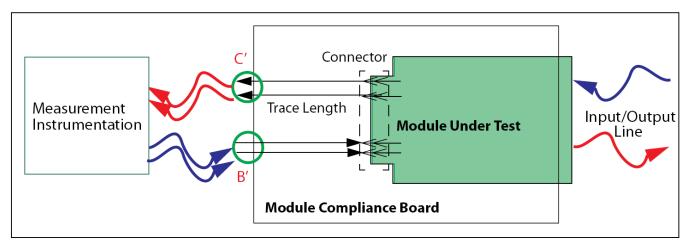

| Module Compliance Board                                                          | 14     | Figure 3  |

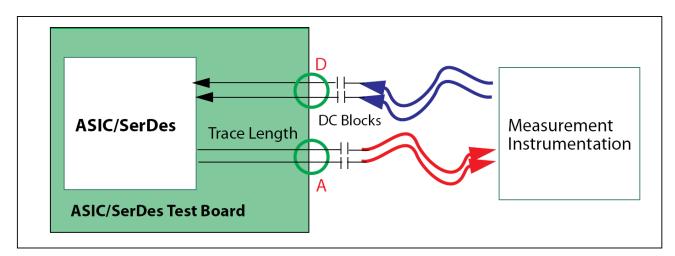

| ASIC/SerDes Test Board                                                           | 15     | Figure 4  |

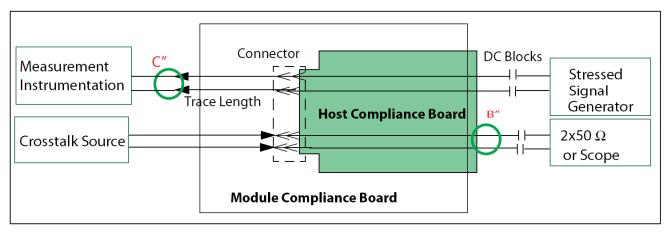

| Host Input Calibration Point C'' and Crosstalk Source Calibration<br>Point B''   | 16     | Figure 5  |

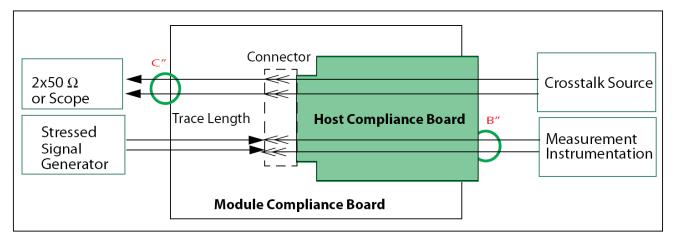

| Module Input Calibration Point B'' and Crosstalk Source<br>Calibration Point C'' | 17     | Figure 6  |

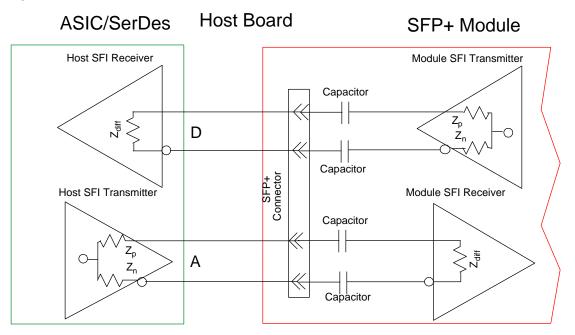

| SFI Termination and AC Coupling                                                  | 18     | Figure 7  |

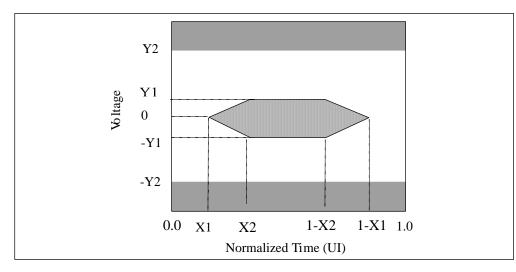

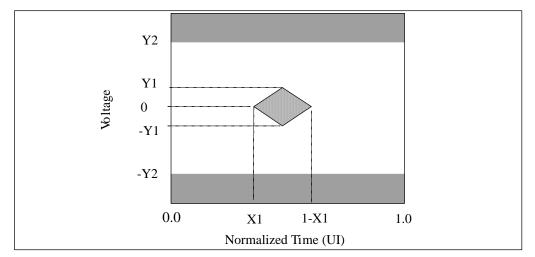

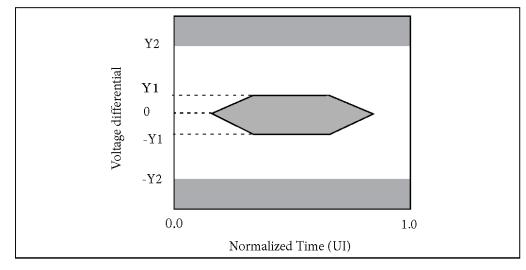

| Transmitter Differential Output Compliance Mask at B and B''                     | 19     | Figure 8  |

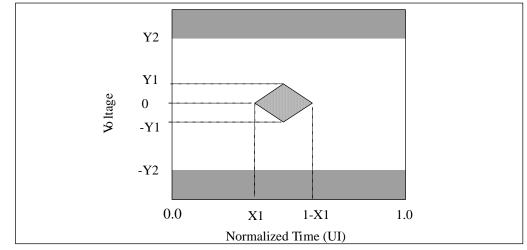

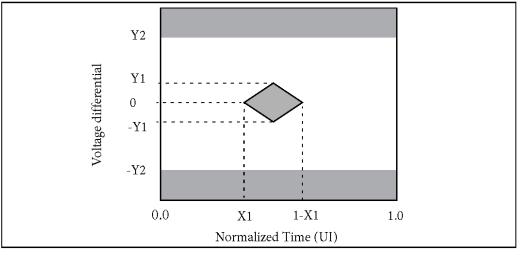

| Host Receiver Input Compliance Mask at C'' Supporting Limiting<br>Module         | 20     | Figure 9  |

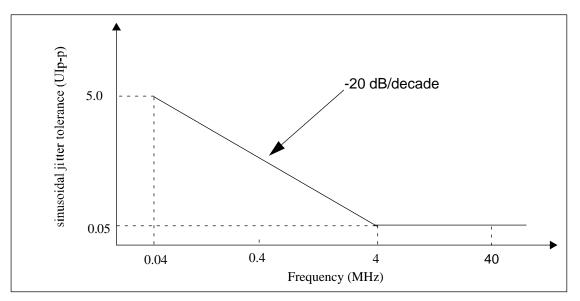

| SR and LR Host Sinusoidal Jitter Tolerance Mask                                  | 21     | Figure 10 |

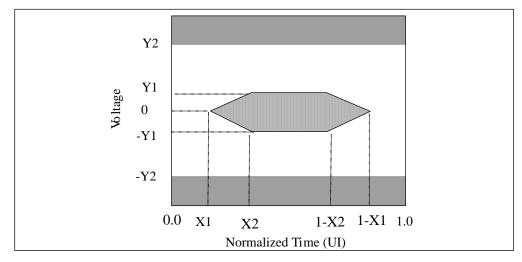

| Module Transmitter Differential Input Compliance Mask at B''                     | 22     | Figure 11 |

| Limiting Module Receiver Differential Output Compliance Mask at C'               | 23     | Figure 12 |

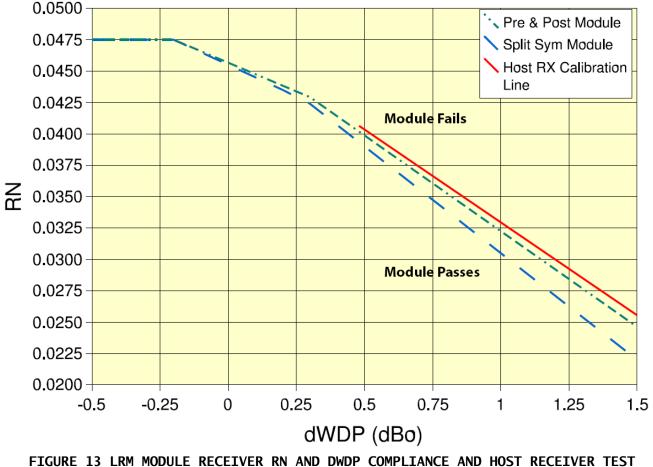

| LRM Module Receiver RN and dWDP Compliance and Host Receiver Test<br>Calibration | 24     | Figure 13 |

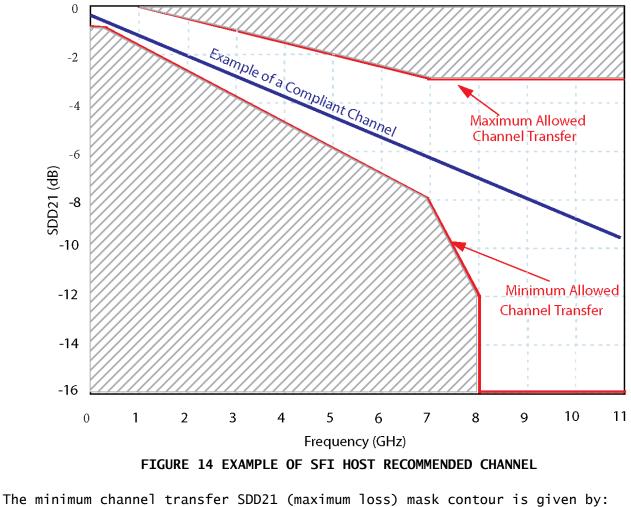

| Example of SFI Host Recommended Channel                                          | 33     | Figure 14 |

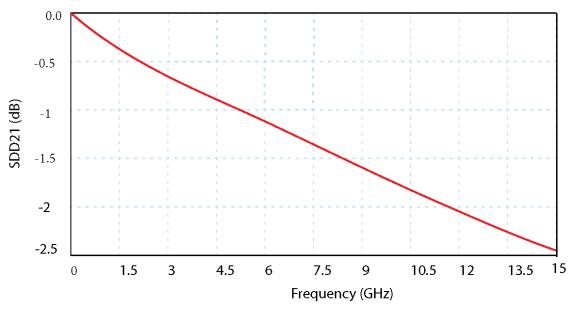

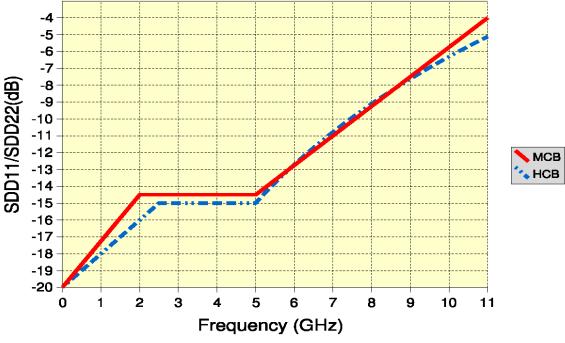

| Approximate Response of Host Compliance Board                                    | 34     | Figure 15 |

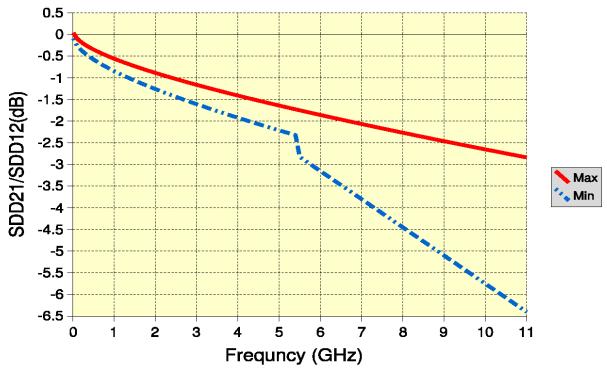

| Approximate Transfer Response of Module Compliance Board                         | 35     | Figure 16 |

| Host Compliance Board Stack-up                                                   | 36     | Figure 17 |

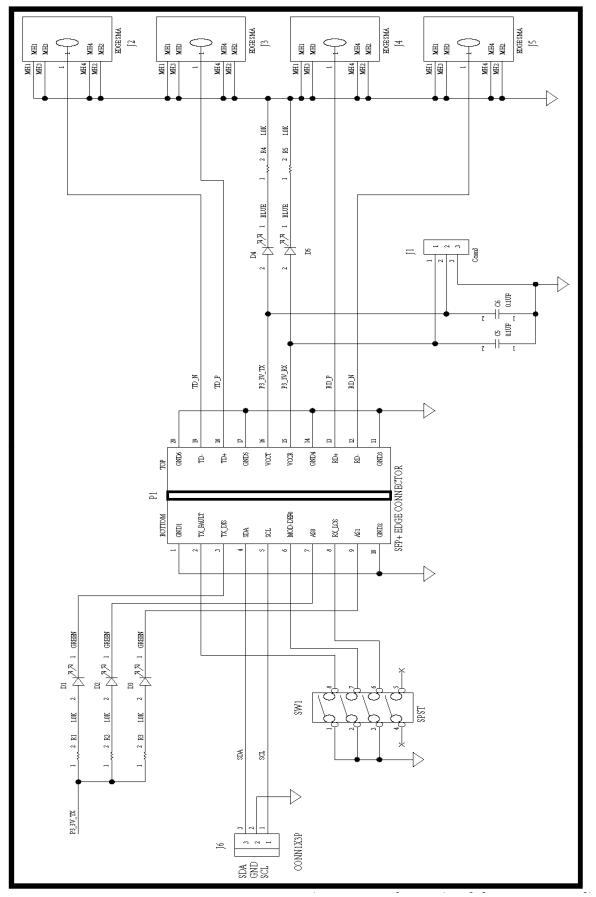

| Schematic of the Host Compliance Board                                           | 37     | Figure 18 |

| Module Compliance Board Stack Up                                                 | 38     | Figure 19 |

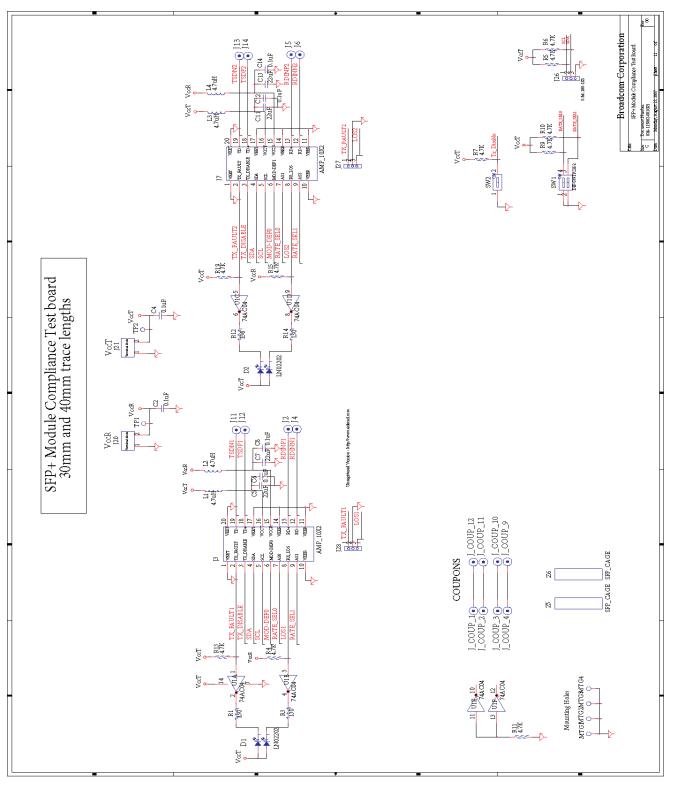

| Schematic of the Module Compliance Board                                         | 39     | Figure 20 |

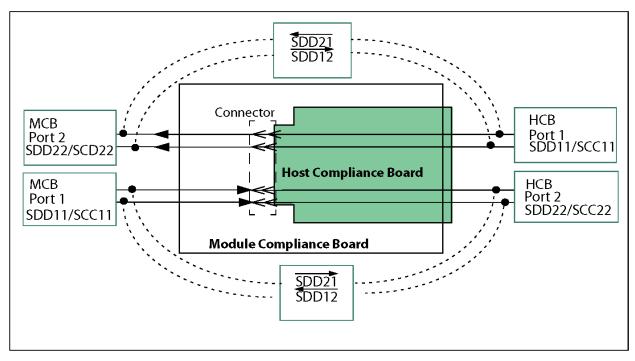

| Measurements Port Definition                                                     | 40     | Figure 21 |

| Maximum Differential Response of Mated MCB and HCB                               | 41     | Figure 22 |

| Mated MCB-HCB Differential Through Response Limits                               | 42     | Figure 23 |

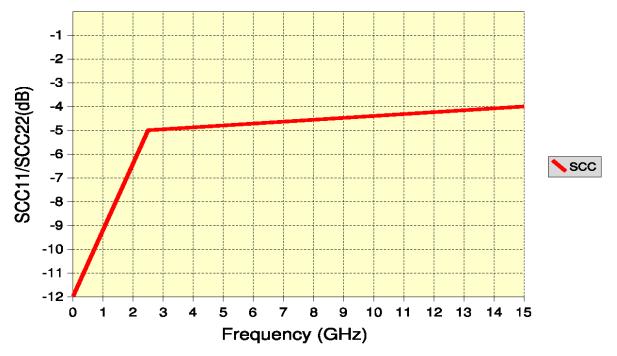

| Maximum Common Mode Response of Mated MCB and HCB                                | 43     | Figure 24 |

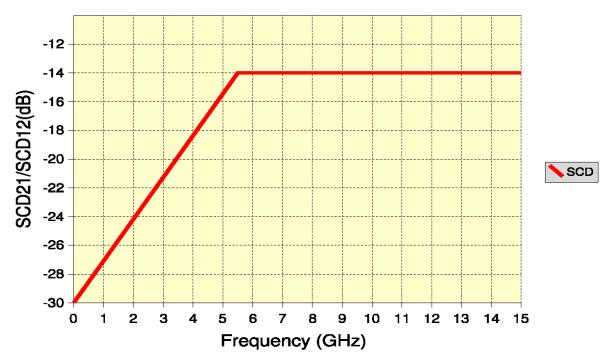

| Maximum Differential to Common Mode Response of mated MCB and HCB                | 44     | Figure 25 |

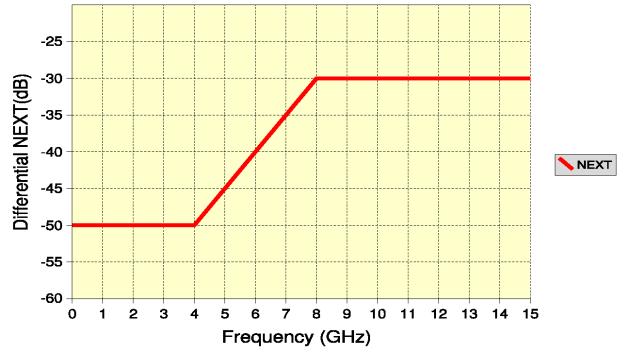

| Maximum Differential NEXT Response of mated MCB and HCB                          | 45     | Figure 26 |

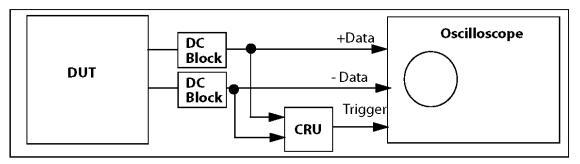

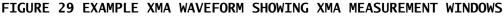

| Eye Mask Measurement Setup - Block Diagram                                       | 46     | Figure 27 |

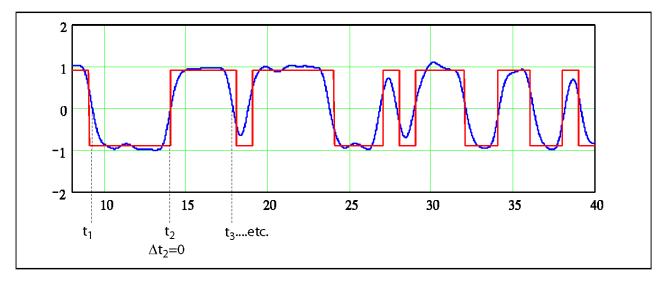

| DDJ Test Method                                                                  | 47     | Figure 28 |

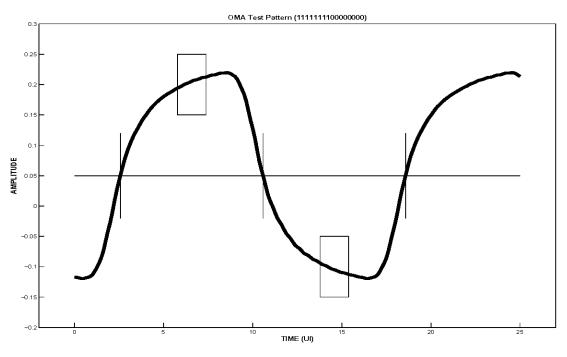

| Example xMA Waveform Showing xMA Measurement Windows                             | 48     | Figure 29 |

| Compliance Signal Generator for Module Transmitter                               | 49     | Figure 30 |

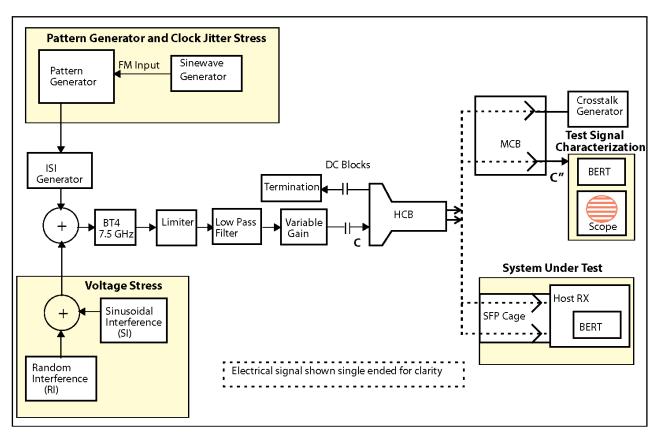

| Jitter Tolerance Test Configuration                                              | 50     | Figure 31 |

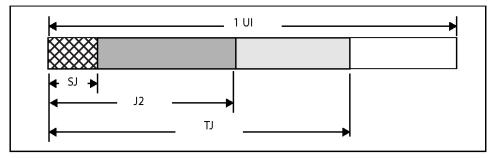

| Stressed Eye Jitter Components                                                   | 51     | Figure 32 |

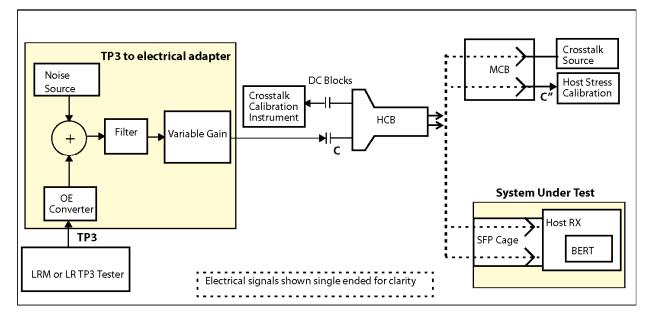

| TP3 to Electrical Adaptor for Host that Operates with Linear                     | 52     | Figure 33 |

| Modules                                                                                   |       |           |

|-------------------------------------------------------------------------------------------|-------|-----------|

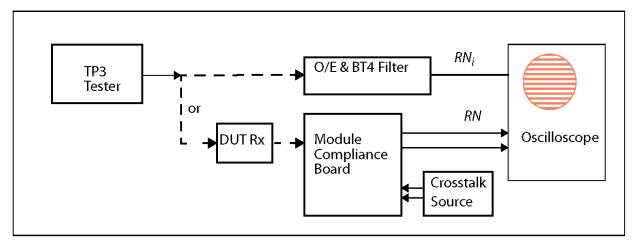

| Linear Module Receiver Noise Test                                                         | 53    | Figure 34 |

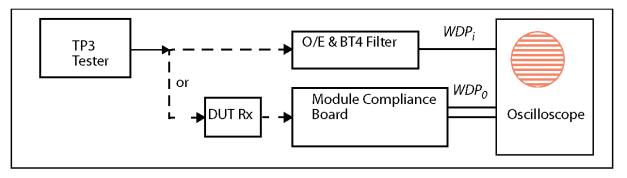

| Module Receiver Waveform Penalty Compliance Test                                          | 54    | Figure 35 |

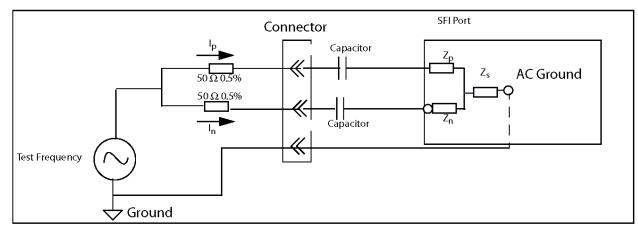

| AC Termination Mismatch Measurement                                                       | 55    | Figure 36 |

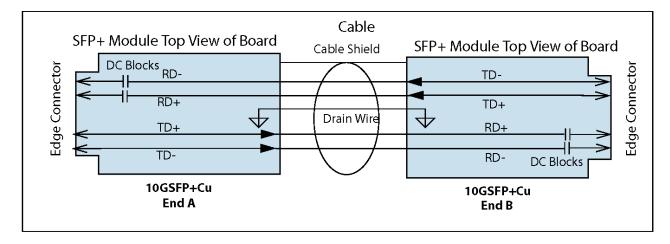

| 10GSFP+Cu Direct Attach Block Diagram                                                     | 59    | Figure 37 |

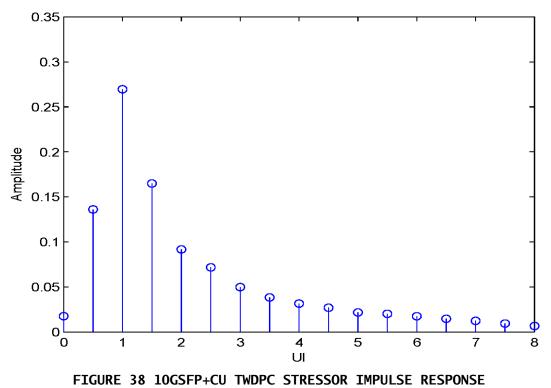

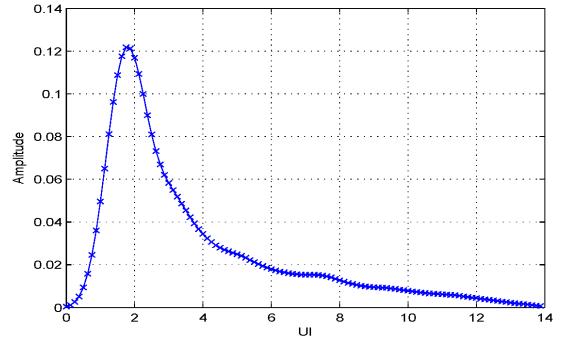

| 10GSFP+Cu TWDPc Stressor Impulse Response                                                 | 60    | Figure 38 |

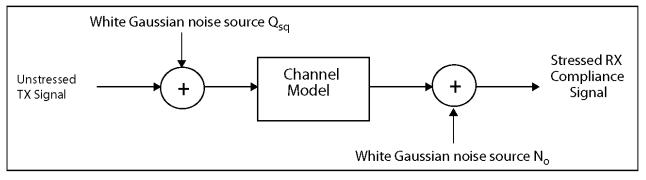

| Block Diagram of Copper Stressor Noise Model                                              | 61    | Figure 39 |

| Stress Generator 1UI Pulse Response with 8x Over-Sampling                                 | 62    | Figure 40 |

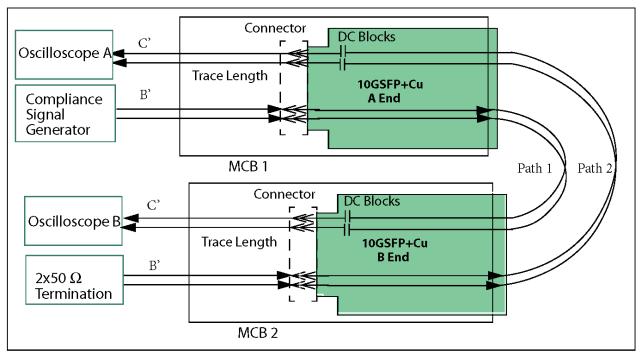

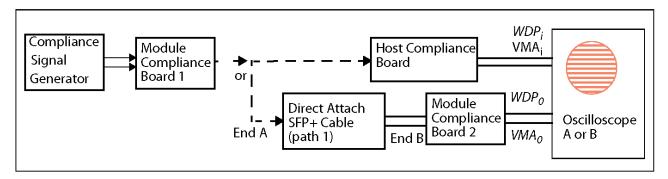

| 10GSFP+ Cable Test Setup                                                                  | 63    | Figure 41 |

| 10GSFP+Cu Cable NEXT dWDP Test Setup                                                      | 64    | Figure 42 |

| SFP+ Host Transmitter Output Mask for 1.25 GBd Operation                                  | 65    | Figure 43 |

| SFP+ Host Receiver Input Mask for 1.25 GBd Operation                                      | 66    | Figure 44 |

|                                                                                           | Table |           |

| SFP+ Standard Compliance                                                                  | 1     | Table 1   |

| Host Board Achievable Trace Length                                                        | 2     | Table 2   |

| SFI Supported Signalling Rates                                                            | 9     | Table 3   |

| SFI Reference Points                                                                      | 10    | Table 4   |

| Host Transmitter Output Electrical Specifications at B                                    | 11    | Table 5   |

| Host Transmitter Output Jitter and Eye Mask Specifications at B                           | 12    | Table 6   |

| Host Receiver Input Electrical Specifications at C and C'                                 | 13    | Table 7   |

| Host Receiver Supporting Limiting Module Input Compliance Test<br>Signal Calibrated at C' | 14    | Table 8   |

| Host Receiver Supporting Linear Module Input Compliance Test<br>Signal Calibrated at C''  | 15    | Table 9   |

| Module Transmitter Input Electrical Specifications at B'                                  | 16    | Table 10  |

| Module Transmitter Input Tolerance Signal Calibrated at B''                               | 17    | Table 11  |

| Module Receiver Output Electrical Specifications at C'                                    | 18    | Table 12  |

| Limiting Module Receiver Output Jitter and Eye Mask Specifications at C'                  | 19    | Table 13  |

| Linear Module Receiver Specifications at C'                                               | 20    | Table 14  |

| SFI Host Interconnect Budget                                                              | 25    | Table 15  |

| ASIC/SerDes Transmitter Output Electrical Specifications at A                             | 26    | Table 16  |

| ASIC/SerDes Receiver Electrical Input Specifications at D                                 | 27    | Table 17  |

| Host Compliance Board Part List                                                           | 28    | Table 18  |

| Module Compliance Board Part List                                                         | 29    | Table 19  |

| Estimated Parameter Values for an Ideal Stressed Signal Generator                         | 30    | Table 20  |

| Target RNi Values                                                                         | 31    | Table 21  |

| SFP+ Host Transmitter Output Specifications at B for Cu                                   | 33    | Table 22  |

| 10GSFP+Cu TWDPc Stressor                                                                  | 34    | Table 23  |

| 10GSFP+ Host receiver input stress Generator at C''                                       | 35    | Table 24  |

| Stress Generator 1 UI Pulse Response with 8x Over-Sampling                                | 36    | Table 25  |

| 10GSFP+Cu Cable Assembly Specifications at B' and C'                                      | 37    | Table 26  |

| INF-8074i Voltage Levels for Reference Only                                               | 38    | Table 27  |

| SFP+ Host Transmitter Requirements to Support 1.25 GBd Mode                               | 39    | Table 28  |

| SFP+ Host Receiver Requirements to Support 1.25 GBd Mode                                  | 40    | Table 29  |

| SFP Module Input and Output Ranges that can be Supported by the SFP+ Host                 | 41    | Table 30  |

CONTENTS

| 1. | Scope<br>1.1 References<br>1.1.1 Industry Documents<br>1.1.2 SFF Specifications<br>1.1.3 Sources<br>1.1.4 Conventions<br>1.1.5 Abbreviations<br>1.2 The SFP+ Supported Standards<br>1.3 SFI Typical PCB Reach (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10<br>10<br>11<br>11<br>11<br>12<br>13<br>14                                                       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 2. | Power and Low Speed Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                 |

| 3. | <pre>High Speed Electrical Specification SFI 3.1 Introduction 3.2 SFI Applications Definition 3.3 SFI Test Points Definition and Measurements 3.3.1 Host Compliance Points 3.3.2 Module Compliance Points 3.3.3 ASIC/SerDes Test Points (Informative) 3.3.4 Host Input Calibration Point 3.4 SFI Termination and DC Blocking 3.5 SFP+ Host System Specifications 3.5.1 Host Transmitter Output Specifications at B 3.5.2 Host Receiver Input Specifications at C and C'' 3.6 SFP+ Module Specifications 3.6.1 Module Transmitter Input Specifications at C'</pre>                                                                                                                                                                                            | 15<br>15<br>15<br>16<br>17<br>17<br>18<br>18<br>18<br>18<br>18<br>19<br>20<br>21<br>25<br>26<br>27 |

| Α. | SFI Channel Recommendation (Informative)<br>A.1 SFI Host Channel General Recommendations<br>A.2 SFI Channel Transfer Recommendations<br>A.3 SFI Channel Return Loss Recommendations<br>A.4 SFI Channel Ripple Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31<br>31<br>33<br>33<br>33                                                                         |

| B. | SFI ASIC/SerDes Specification (Informative)<br>B.1 Introduction<br>B.2 SFI ASIC/SerDes Transmitter Output Specifications At A (Informative)<br>B.3 SFI ASIC/SerDes Receiver Input Specifications At D (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34<br>34<br>34<br>34                                                                               |

| с. | <pre>Application Reference Boards (Normative)<br/>C.1 Compliance Boards<br/>C.1.1 Host Compliance Board Transfer Characteristics<br/>C.1.2 Module Compliance Board Transfer Characteristics<br/>C.1.3 ASIC/SerDes Test Board Transfer Characteristics<br/>C.2 Host Compliance Board<br/>C.2.1 Host Compliance Board Material And Layer Stack-Up<br/>C.2.2 Host Compliance Board Partlist<br/>C.2.3 HCB Gerber Files<br/>C.2.4 Schematic of Host Compliance Board<br/>C.3 Module Compliance Board<br/>C.3.1 Module Compliance Board Material And Layer Stack-Up<br/>C.3.2 Schematic of Module Compliance Board<br/>C.3.3 Module Compliance Board Partlist<br/>C.3.4 MCB Gerber Files<br/>C.4 Specifications For Mated Host and Module Compliance Boards</pre> | 36<br>36<br>37<br>38<br>38<br>38<br>39<br>39<br>39<br>41<br>41<br>41<br>43<br>43<br>43             |

| D. | Test Methodology And Measurement (Normative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                 |

## **Published**

|    | D.1 Introduction<br>D.1.1 Test Patterns<br>D.2 Eye Mask Compliance<br>D.2.1 Example Calculations For SX10^(-5) Hit Ratio<br>D.3 Data Dependent Jitter (DDJ) And Pulse Width Shrinkage (DDPWS)<br>D.3.1 Duty Cycle Distortion (DCD)<br>D.4 Uncorrelated Jitter (UJ)<br>D.5 99% Jitter (J2) and Total Jitter (TJ)<br>D.6 Rise And Fall Times<br>D.7 Voltage Modulation Amplitude (VMA)<br>D.8 Relative Noise (RN)<br>D.9 Waveform Distortion Penalty (WDP)<br>D.10 Electrical Compliance Signal at B'' for the SFP+ Module Transmitter<br>D.11 Test Method for a Host Receiver for a Limiting Module<br>D.11.1 Test Equipment and Setup<br>D.11.2 Stressed-Eye Jitter Characteristics<br>D.11.3 Calibration<br>D.11.4 Calibration Procedure<br>D.11.5 Test Procedure<br>D.13 Test Method for a Host Receiver with a Linear Module<br>D.13.1 Test Description and Procedure for Host Receiver for Linear Module<br>D.13.2 Host Linear Tester Calibration<br>D.14.4 Linear Module Receiver Compliance Tests<br>D.14.1 Linear Module Receiver Distortion Penalty Compliance Test<br>D.14.2 Linear Module Receiver Output Differential Peak-Peak Voltage<br>D.15.1 Definition of AC Common Mode Voltage<br>D.15.1 Definition of AC Common Mode Voltage<br>D.15.2 AC Common Mode Generation Test<br>D.15.3 AC Common Mode Golerance Test<br>D.15.3 AC Common Mode Golerance Test<br>D.15.1 Definition of AC common Mode Voltage<br>D.15.2 AC Common Mode Golerance Test<br>D.15.3 AC Common Mode Golerance Test<br>D.16 Termination Mismatch | 49<br>49<br>50<br>51<br>52<br>53<br>55<br>55<br>57<br>57<br>59<br>60<br>61<br>23<br>34<br>56<br>66<br>66<br>66<br>66<br>66<br>66<br>66<br>66<br>66<br>66 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| E. | <pre>SFP+ Direct Attach Cable Specifications "10GSFP+Cu" (Optional)<br/>E.1 10GSFP+Cu Direct Attach Construction<br/>E.2 SFP+ Host Output Specifications For Passive Direct Attach Cables<br/>E.2.1 Transmitter Stressor</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68<br>68<br>69<br>69                                                                                                                                     |

|    | <ul> <li>E.3 SFP+ Host Receiver Supporting 10GSFP+Cu Input Compliance Test Signal Calibrated at C''</li> <li>E.3.1 Copper Host Receiver Specifications</li> <li>E.3.2 Copper Host Stress Generator 1 UI Pulse Response</li> <li>E.4 SFP+ Passive Direct Attach Cable Assembly Specifications</li> <li>E.4.1 SFP+ Direct Attach Cable Test Setup</li> <li>E.4.2 Cable dWDP Test Procedure</li> <li>E.4.3 Cable NEXT Measurement Procedure</li> <li>E.4.4 VMA to Crosstalk Ratio (VCR)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70<br>70<br>71<br>73<br>74<br>75<br>76<br>76                                                                                                             |

| F. | 1.25 GBd Operation Support (Optional)<br>F.1 Introduction<br>F.2 SFP+ Host Operation Guideline For Supporting Classic SFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77<br>77<br>77                                                                                                                                           |

| G. | Matlab Code For TWDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79                                                                                                                                                       |

FIGURES

| FIGURES                                                                           |          |

|-----------------------------------------------------------------------------------|----------|

| Figure 1 SFI Application Reference Model                                          | 15       |

| Figure 2 Host Compliance Board                                                    | 16       |

| Figure 3 Module Compliance Board                                                  | 17       |

| Figure 4 ASIC/SerDes Test Board                                                   | 17       |

| Figure 5 Host Input Calibration Point C'' and Crosstalk Source Calibration Point  |          |

| B' 18                                                                             |          |

|                                                                                   |          |

| Figure 6 Module Input Calibration Point B'' and Crosstalk Source Calibration Poin | ητ       |

| C'' 18                                                                            |          |

| Figure 7 SFI Termination and AC Coupling                                          | 19       |

| Figure 8 Transmitter Differential Output Compliance Mask at B and B''             | 21       |

| Figure 9 Host Receiver Input Compliance Mask at C'' Supporting Limiting Module    | 23       |

| Figure 10 SR and LR Host Sinusoidal Jitter Tolerance Mask                         | 24       |

| Figure 11 Module Transmitter Differential Input Compliance Mask at B''            | 27       |

| Figure 12 Limiting Module Receiver Differential Output Compliance Mask at C'      | 29       |

| Figure 13 LRM Module Receiver RN and dWDP Compliance and Host Receiver Test       |          |

| Calibration                                                                       | 30       |

| Figure 14 Example of SFI Host Recommended Channel                                 | 32       |

|                                                                                   | 37       |

| Figure 15 Approximate Response of Host Compliance Board                           |          |

| Figure 16 Approximate Transfer Response of Module Compliance Board                | 38       |

| Figure 17 Host Compliance Board Stack-up                                          | 39       |

| Figure 18 Schematic of the Host Compliance Board                                  | 40       |

| Figure 19 Module Compliance Board Stack Up                                        | 41       |

| Figure 20 Schematic of the Module Compliance Board                                | 42       |

| Figure 21 Measurements Port Definition                                            | 44       |

| Figure 22 Maximum Differential Response of Mated MCB and HCB                      | 44       |

| Figure 23 Mated MCB-HCB Differential Through Response Limits                      | 45       |

| Figure 24 Maximum Common Mode Response of Mated MCB and HCB                       | 46       |

| Figure 25 Maximum Differential to Common Mode Response of mated MCB and HCB       | 47       |

| Figure 26 Maximum Differential NEXT Response of mated MCB and HCB                 | 48       |

| Figure 27 Eye Mask Measurement Setup - Block Diagram                              | 50       |

| Figure 28 DDJ Test Method                                                         | 50<br>51 |

|                                                                                   | 54       |

| Figure 29 Example xMA Waveform Showing xMA Measurement Windows                    |          |

| Figure 30 Compliance Signal Generator for Module Transmitter                      | 56       |

| Figure 31 Jitter Tolerance Test Configuration                                     | 58       |

| Figure 32 Stressed Eye Jitter Components                                          | 58       |

| Figure 33 TP3 to Electrical Adaptor for Host that Operates with Linear Modules    | 62       |

| Figure 34 Linear Module Receiver Noise Test                                       | 64       |

| Figure 35 Module Receiver Waveform Penalty Compliance Test                        | 65       |

| Figure 36 AC Termination Mismatch Measurement                                     | 67       |

| Figure 37 10GSFP+Cu Direct Attach Block Diagram                                   | 68       |

| Figure 38 10GSFP+Cu TWDPc Stressor Impulse Response                               | 69       |

| Figure 39 Block Diagram of Copper Stressor Noise Model                            | 71       |

| Figure 40 Stress Generator 1UI Pulse Response with 8x Over-Sampling               | 72       |

| Figure 41 10GSFP+ Cable Test Setup                                                | 75       |

| Figure 42 10GSFP+Cu Cable NEXT dWDP Test Setup                                    | 75       |

| Figure 43 SFP+ Host Transmitter Output Mask for 1.25 GBd Operation                | 78       |

| Figure 44 SFP+ Host Receiver Input Mask for 1.25 GBd Operation                    | 78<br>78 |

| I Iguie 44 SIRT HOSE RECEIVED INPUT MASK TOT I.23 ODU OPETALTON                   | 10       |

|                                                                                   |          |

#### TABLES

Table 1 SFP+ Standard Compliance14Table 2 Host Board Achievable Trace Length14Table 3 SFI Supported Signalling Rates15Table 4 SFI Reference Points16Table 5 Host Transmitter Output Electrical Specifications at B20Table 6 Host Transmitter Output Jitter and Eye Mask Specifications at B21Table 7 Host Receiver Input Electrical Specifications at C and C''22Table 8 Host Receiver Supporting Limiting Module Input Compliance Test Signal

| Calibrated at C''                                                            | 23 |

|------------------------------------------------------------------------------|----|

| Table 9 Host Receiver Supporting Linear Module Input Compliance Test Signal  |    |

| Calibrated at C''                                                            | 25 |

| Table 10 Module Transmitter Input Electrical Specifications at B'            | 26 |

| Table 11 Module Transmitter Input Tolerance Signal Calibrated at B''         | 27 |

| Table 12 Module Receiver Output Electrical Specifications at C'              | 28 |

| Table 13 Limiting Module Receiver Output Jitter and Eye Mask Specifications  |    |

| Table 14 Linear Module Receiver Specifications at C'                         | 29 |

| Table 15 SFI Host Interconnect Budget                                        | 31 |

| Table 16 ASIC/SerDes Transmitter Output Electrical Specifications at A       | 35 |

| Table 17 ASIC/SerDes Receiver Electrical Input Specifications at D           | 35 |

| · · ·                                                                        | 39 |

| Table 18 Host Compliance Board Part List                                     |    |

| Table 19 Module Compliance Board Part List                                   | 43 |

| Table 20 Estimated Parameter Values for an Ideal Stressed Signal Generator   | 57 |

| Table 21 Target RNi Values                                                   | 65 |

| Table 22 SFP+ Host Transmitter Output Specifications at B for Cu             | 69 |

| Table 23 10GSFP+Cu TWDPc Stressor                                            | 70 |

| Table 24 10GSFP+ Host receiver input stress Generator at C''                 | 71 |

| Table 25 Stress Generator 1 UI Pulse Response with 8x Over-Sampling          | 73 |

| Table 26 10GSFP+Cu Cable Assembly Specifications at B' and C'                | 74 |

| Table 27 INF-8074i Voltage Levels for Reference Only                         | 77 |

| Table 28 SFP+ Host Transmitter Requirements to Support 1.25 GBd Mode         | 77 |

| Table 29 SFP+ Host Receiver Requirements to Support 1.25 GBd Mode            | 78 |

| Table 30 SFP Module Input and Output Ranges that can be Supported by the SFP |    |

|                                                                              |    |

SFF Committee --

#### SFP+ 10 Gb/s Electrical Interface

#### 1. Scope

This specification defines the electrical interfaces and their test methods between the SFP+ module and host board for operation up to 11.1 GBd. The high speed electrical interface between the host and SFP+ module is called SFI. SFI simplifies the module and leverages host based transmit pre-emphasis and host based receive equalization to overcome PCB and external media impairments.

SFI typically operates with one connector at the module interface and up to about 200 mm of improved FR4 material or 150 mm of standard FR4. The electrical interface is based on high speed, low voltage AC coupled logic with a nominal differential impedance of 100 Ohms.

The SFP+ specifications includes management, connector (SFF-8071), mechanical (SFF-8432), power supply and low speed signalling (SFF-8419), high speed signalling, and appendices providing parameter and test board definitions, and implementation and measurement descriptions

SFP+ modules are hot pluggable and active connections are powered by individual power connections for the transmitter (VccT) and the receiver (VccR). Multiple modules can share a single 3.3 V power supply with individual filtering for each VccT and VccR. Detailed power supply specifications are found in SFF-8419.

All SFP+ module compliance points are defined and measured through the mated reference test card as defined by C.3 . All SFP+ host compliance points are defined and measured through the mated reference test card as defined by C.2 .

The SFP+ module could be an electrical-to-optical or an electrical-to-electrical device intended to support one or more of the applications listed in Table 1.

It is expected that a range of SFP+ modules will operate on single-mode fiber, multimode fiber, and SFP+ electrical cable assemblies.

SFP+ compliant hosts are permitted to support just linear modules, just limiting modules, or both linear and limiting modules. Linear modules are modules which contain a linear receiver. Limiting modules are modules which contain a limiting receiver. Although not required, host supporting linear specifications are encouraged to support 10GSFP+Cu direct attach cables (Appendix E). For other copper variants see SFF-8461.

## 1.1 References

### 1.1.1 Industry Documents

| IEEE 802.3   | IEEE Standard for Ethernet *                              |

|--------------|-----------------------------------------------------------|

| INCITS 450   | FC-PI-4 (Fibre Channel Physical Interface - 4 (T11/1647D) |

| INCITS 364   | FC-10GFC (10 Gb/s)                                        |

| INCITS TR-46 | FC-MJSQ - Methodologies for Jitter and Signal Quality     |

| OIF-CEI      | Optical Internetworking Forum - Common Electrical I/O     |

| INF-8074i    | SFP (Small Formfactor Pluggable) 1 Gb/s Transceiver       |

| INF-8077i    | XFP 10 Gb/s 1X Pluggable Module                           |

| SFF-8071     | SFP+ 1X 0.8mm Card Edge Connector                         |

| SFF-8083     | SFP+ 1X 10 Gb/s Pluggable Transceiver Solution (SFP10)    |

| SFF-8079     | SFP Rate and Application Selection                        |

| SFF-8089     | SFP Rate and Application Codes                            |

| SFF-8419     | SFP+ Power and Low Speed Interface plus Matlab Code       |

| SFF-8431 | SFP+ 10 Gb/s and Low Speed Electrical Interface |

|----------|-------------------------------------------------|

| SFF-8432 | SFP+ 10 Gb/s Module and Cage                    |

| SFF-8472 | Management Interface for SFP+                   |

\* Relevant clauses are 49, 10GBASE-R LAN PHY; 50, 10GBASE-W WAN PHY; 52, 10 Gigabit Ethernet serial PMDs; and 68, 10GBASE-LRM)

## 1.1.2 SFF Specifications

There are several projects active within the SFF Committee. The complete list of specifications which have been completed or are still being worked on are listed in the specification at <u>ftp://ftp.seagate.com/sff/SFF-8000.TXT</u>

## 1.1.3 Sources

Those who join the SFF Committee as an Observer or Member receive electronic copies of the minutes and SFF specifications (http://www.sffcommittee.com/ie/join.html).

Copies of ANSI standards may be purchased from the InterNational Committee for Information Technology Standards (<u>http://www.techstreet.com/incitsgate.tmpl</u>).

## 1.1.4 Conventions

The dimensioning conventions are described in ANSI-Y14.5M, Geometric Dimensioning and Tolerancing. All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

The ISO convention of numbering is used i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point. This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

## 1.1.5 Abbreviations

| 64B/66<br>B | Data encoded with 64B/66B encoder as defined by the IEEE Std. 802.3 CL 49.                                                                                                                                                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BER         | bit error ratio                                                                                                                                                                                                                                                                                                                |

| CDR         | clock and data recovery                                                                                                                                                                                                                                                                                                        |

| CRU         | clock recovery unit                                                                                                                                                                                                                                                                                                            |

| dB          | decibel. 10*log10(ratio of power quantities). Powers can be electrical or optical. Conventional usage. See also dBe and dBo.                                                                                                                                                                                                   |

| dBe         | Specific case of dB where signals are electrical. 10*log10(ratio of electrical power quantities). 20*log10(ratio of voltage quantities) can be used if reference impedances are equal.                                                                                                                                         |

| dBm         | decibel (relative to 1 mW)                                                                                                                                                                                                                                                                                                     |

| dBo         | Specific case of dB where the signals are in optical power. 10*log10(ratio<br>of optical power quantities). Also, in certain cases with electrical<br>signals relating to linear optical modules, where it is expected that<br>electrical voltage is in proportion to optical power, 10*log10(ratio of<br>voltage quantities). |

| DCD         | Duty cycle distortion                                                                                                                                                                                                                                                                                                          |

| DDPWS       | Data Dependent Pulse Width Shrinkage                                                                                                                                                                                                                                                                                           |

| DDJ         | Data Dependent Jitter                                                                                                                                                                                                                                                                                                          |

| dRN         | Difference of Relative noise see Appendix D                                                                                                                                                                                                                                                                                    |

| DUT         | device under test                                                                                                                                                                                                                                                                                                              |

| dWDP        | Difference of the waveform distortion penalty of an optical receiver                                                                                                                                                                                                                                                           |

| dWDPc       | Difference of the waveform distortion penalty of an electrical cable assembly                                                                                                                                                                                                                                                  |

| EMC         | electromagnetic compatibility                                                                                                                                                                                                                                                                                                  |

| EMI         | electromagnetic Interference                                                                                                                                                                                                                                                                                                   |

| FC          | Fibre Channel                                                                                                                                                                                                                                                                                                                  |

| h           | hexadecimal notation                                                                                                                                                                                                                                                                                                           |

| НСВ         | Host Compliance Board                                                                                                                                                                                                                                                                                                          |

| IEEE        | Institute of Electrical and Electronics Engineers                                                                                                                                                                                                                                                                              |

| ITU-T       | ITU Telecommunication Standardization Sector                                                                                                                                                                                                                                                                                   |

| Gbit        | gigabit = $10^{(9)}$ bits                                                                                                                                                                                                                                                                                                      |

| GBd         | Gigabaud                                                                                                                                                                                                                                                                                                                       |

| J2          | 99% Jitter                                                                                                                                                                                                                                                                                                                     |

| LRM         | IEEE 802.3 CL68 Physical Layer Specifications for 10 Gb/s using 10GBASE-R encoding and long wavelength optics for multimode fiber                                                                                                                                                                                              |

| MCB         | Module Compliance Board                                                                                                                                                                                                                                                                                                        |

| OMA         | optical modulation amplitude                                                                                                                                                                                                                                                                                                   |

| PCB         | printed circuit board                                                                                                                                                                                                                                                                                                          |

| PRBS9       | Pseudo-Random Bit Sequence 2e9-1, see D.1.1                                                                                                                                                                                                                                                                                    |

| PRBS31      | Pseudo-Random Bit Sequence 2e31-1, see D.1.1                                                                                                                                                                                                                                                                                   |

| Qsq         | a measure of SNR, see D.8 and IEEE 802.3.68.6.7                                                                                                                                                                                                                                                                                |

| RI          | random interference                                                                                                                                                                                                                                                                                                            |

| RMS         | root mean square                                                                                                                                                                                                                                                                                                               |

| RN          | relative noise                                                                                                                                                                                                                                                                                                                 |

| Rx          | receiver                                                                                                                                                                                                                                                                                                                       |

| Rx_LOS      | Loss of signal same as defined in FC PI-4 and the inverse of signal detect (SD) in 802.3                                                                                                                                                                                                                                       |

| RSS         | Root Sum of Squares                                                                                                                                                                                                                                                                                                            |

| SD     | Signal Detect                                                                                         |

|--------|-------------------------------------------------------------------------------------------------------|

| SD     | Signal Detect                                                                                         |

| SerDes | Serializer/Deserializer                                                                               |

| SFI    | SFP+ high speed serial electrical interface                                                           |

| SNR    | signal-to-noise ratio                                                                                 |

| VccT   | Module positive power supply rail for the transmitter                                                 |

| VccR   | Module positive power supply rail for the receiver                                                    |

| VMA    | voltage modulation amplitude                                                                          |

| Tx     | transmitter                                                                                           |

| TWDP   | Transmitter Waveform Distortion Penalty for an optical transmitter                                    |

| TWDPc  | Transmitter Waveform Distortion Penalty of a host transmitter supporting an electrical cable assembly |

| UI     | unit interval = 1 symbol period                                                                       |

| UJ     | Uncorrelated Jitter                                                                                   |

| WDP    | Waveform distortion penalty                                                                           |

| WDPc   | Waveform distortion penalty for an electrical cable assembly                                          |

## 1.2 The SFP+ Supported Standards

An SFP+ module may comply with any combination of the standards shown in Table 1, and may be suitable for other or future standards. This specification does not preclude operation at other signalling rates not listed in this table, such as 2.125 GBd for 2GFC, or 4.25 GBd for 4GFC.

Due to the possibility of insertion of classic SFP modules into a host designed for SFP+ the damage threshold of the host for the input signal at C (see Figure 2) shall be at least 2000 mV peak to peak differential.

|                   | IA       | BLE I SER+ | STANDARD | CUMPLIANC | -     |          |          |

|-------------------|----------|------------|----------|-----------|-------|----------|----------|

| Standard          | Sign     | High       | High     | Low       | Low   | Manage   | Mech     |

|                   | aling    | Speed      | Speed    | Speed     | Speed | ment     | anical/  |

|                   | Rate     | Serial     | Serial   | Elect     | Test  |          | Conn     |

|                   | (GBd)    | Interface  | Test     | rical     | Meth  |          | ector    |

|                   |          |            | Method   | Defin     | ods   |          |          |

|                   |          |            |          | itions    |       |          |          |

| IEEE 802.3        | 1.25     | 802.3      |          |           |       |          |          |

| Clause 38 or      |          | Clause 38  |          |           |       |          |          |

| Clause 59 (1      |          | or 59      |          |           |       |          |          |

| Gb/s Ethernet)    |          | Appen      |          |           |       |          |          |

|                   |          | dix F      |          |           |       |          |          |

| 1 GFC             | 1.0625   | FC-PH      | FC-PH    |           |       |          |          |

| 2 GFC             | 2.125    | FC-PI      | FC-PI    |           |       |          |          |

| 4 GFC             | 4.25     | FC-PI-2    | FC-PI-2  |           |       |          |          |

| 8 GFC *           | 8.5      | FC-PI-5    | FC-PI-5  |           |       |          |          |

| 16 GFC            | 14.025   | FC-PI-5    | FC-PI-5  |           |       |          |          |

| 32 GFC            | 28.05    | FC-PI-6    | FC-PI-6  |           |       |          |          |

| 10GSFP+Cu         | 10.3125  | Section 3  | Appen    |           |       |          |          |

|                   |          | Appen      | dix D    |           |       |          |          |

|                   |          | dix E      | Appen    |           |       |          |          |

|                   |          |            | dix E    | SFF-      | SFF-  | SFF-8419 | SFF-8432 |

| IEEE 802.3        | 10.3125  |            |          | 8419      | 8419  | SFF-8472 | SFF-8071 |

| Clause 52 (10     |          |            |          |           |       | SFF-8079 |          |

| Gb/s Ethernet     |          |            |          |           |       | SFF-8089 |          |

| LAN PHY)          |          |            |          |           |       |          |          |

| IEEE 802.3        | 9.95328  | Section 3  | Appen    |           |       |          |          |

| Clause 52 (10     |          |            | dix D    |           |       |          |          |

| Gb/s Ethernet     |          |            |          |           |       |          |          |

| WAN PHY)          |          |            |          |           |       |          |          |

| IEEE 802.3        | 10.3125  |            |          |           |       |          |          |

| Clause 68 (LRM)   |          |            |          |           |       |          |          |

| 10 GFC            | 10.51875 |            |          |           |       |          |          |

| 10GBASE-R (IEEE   | 11.10    |            |          |           |       |          |          |

| 802.3 Clause 49)  |          |            |          |           |       |          |          |

| Encapsulated in   |          |            |          |           |       |          |          |

| G.709 ODU-2       |          |            |          |           |       |          |          |

| Frame (FEC)       |          |            |          |           |       |          |          |

| * 8GFC specificat |          |            |          |           | DT 4  |          | •        |

#### TABLE 1 SFP+ STANDARD COMPLIANCE

## 1.3 SFI Typical PCB Reach (Informative)

The SFI channel may be implemented with either microstrip or stripline structures. Example host board designs with typical PCB trace reaches are shown in Table 2. Detailed channel properties and recommendations are documented in Appendix A

| Туре         | Material      | Trace | Loss    | Copper    | Copper    | Trace  |  |  |  |  |

|--------------|---------------|-------|---------|-----------|-----------|--------|--|--|--|--|

|              |               | Width | Tangent | Thickness | Thickness | Length |  |  |  |  |

|              |               | (mm)  | _       | (oz) *    | (um)      | (mm)   |  |  |  |  |

| Microstrip   | FR4-6/8       | 0.3   | 0.022   | 1.0       | 35.0      | 200    |  |  |  |  |

|              | Nelco 4000-13 | 0.3   | 0.016   | 1.0       | 35.0      | 300    |  |  |  |  |

| Stripline    | FR4-6/8       | 0.125 | 0.022   | 0.5       | 17.5      | 150    |  |  |  |  |

|              | Nelco 4000-13 | 0.125 | 0.016   | 0.5       | 17.5      | 200    |  |  |  |  |

| * Copper (oz |               |       |         |           |           |        |  |  |  |  |

## TABLE 2 HOST BOARD ACHIEVABLE TRACE LENGTH

#### 2. Power and Low Speed Electrical Specifications

Section 2, Section 4, Appendix D.17 and Appendix G of SFF-8431 SFP+ 10 Gb/s and Low Speed Electrical Interface were removed to create the SFF-8419 specification. This was done to separate module management's low speed interface from 10 Gb/s operation, so SFF-8419 could be referenced by later generations of a higher speed.

## 3. High Speed Electrical Specification SFI

#### 3.1 Introduction

SFI signalling is based on differential high speed low voltage logic with ACcoupling in the module. SFI was developed with the primary goal of low power and low electromagnetic interference (EMI). To satisfy this requirement the nominal differential signal levels are ~500 mV p-p with edge speed control to reduce EMI. SFP+ compliant hosts are allowed to support just linear modules, just limiting modules, or both linear and limiting modules.

## 3.2 SFI Applications Definition

The application reference model for SFI connects a high speed ASIC/SERDES to the SFP+ module as shown in Figure 1.

The SFI interface is designed to support IEEE 802.3 10Gig standards Clauses 49, 50, and 51, and 10GFC. For all other FC signalling rates see FC-PI-4. SFI supported signalling rates are listed in Table 3. SFP+ compliant modules and hosts may support one or more of the signalling rates listed in Table 3. For 10GSFP+Cu (direct attach copper) specifications and applications reference model, see Appendix E.

| Standard                   | Description          | Signaling Rate | Unit |

|----------------------------|----------------------|----------------|------|

| IEEE std-802.3 Clause 50   | 10GBASE-W WAN PHY    | 9.95328        | GBd  |

| IEEE std-802.3 Clause 49   | 10GBASE-R LAN PHY    | 10.3125        | GBd  |

| Fibre Channel - 10 Gigabit | 10GFC                | 10.51875       | GBd  |

| 10Gig Ethernet with FEC    | 10GBASE-R over G.709 | 11.10          | GBd  |

#### TABLE 3 SFI SUPPORTED SIGNALLING RATES

The SFI interface operates from 9.95 to 11.1 GBd.

Note: SFF-8083 contents transferred to SFF-8071 FIGURE 1 SFI APPLICATION REFERENCE MODEL

#### 3.3 SFI Test Points Definition and Measurements

SFI reference compliance test points are defined with the Host Compliance Board and the Module Compliance Board for measurement consistency, see Appendix C. The reference test boards provide a set of overlapping measurements for ASIC/SerDes, module, and host validation to ensure interoperability. For improved measurement accuracy the actual reference test card responses may be calibrated out of the measurements and replaced with functions that represent the ideal responses defined in Appendix C for the reference test cards.

Points A, B, C, and D require AC coupled test equipment. All SFI test equipment must have 50 Ohms single ended impedance on all test ports.

The reference impedance for differential measurements and S-parameters is 100 Ohms, and the reference impedance for common mode measurements and S-parameters is 25 Ohms.

The bandwidth of measurement instrument shall be 12 GHz unless specified otherwise. SFI reference points are listed in Table 4.

| Compliance point         | Designation            |

|--------------------------|------------------------|

| ASIC/SerDes output       | A                      |

| Host output              | В                      |

| Host input               | С                      |

| ASIC/SerDes input        | D                      |

| Module input             | В'                     |

| Module output            | C'                     |

| Module input calibration | B'' (double quotation) |

| Host input calibration   | C'' (double quotation) |

TABLE 4 SFI REFERENCE POINTS

## 3.3.1 Host Compliance Points

Host system transmitter and receiver compliance are defined by tests in which a Host Compliance Board is inserted as shown in place of the SFP+ module. The Host Compliance Board meets the specifications of Appendix C. The compliance points are B and C.

## FIGURE 2 HOST COMPLIANCE BOARD

SFP+ host compliance points are defined as the following:

- B Host transmitter output at the output of the Host Compliance Board. Specifications for B are given in Section 3.5.1.

- C Host receiver input at the input of the Host Compliance Board. Specifications for C are given in Section 3.5.2.

## **Published**

## 3.3.2 Module Compliance Points

Module transmitter and receiver compliance are defined by tests in which the module is inserted into the Module Compliance Board. The Module Compliance Board meets the specifications of Appendix C. The compliance points for the module are B' and C'.

FIGURE 3 MODULE COMPLIANCE BOARD

SFP+ module compliance points are defined as the following:

- B' SFP+ module transmitter input at the input of the Module Compliance Board. Specifications for B' are given in Section 3.6.1.

- C' SFP+ module receiver output at the output of the Module Compliance Board. Specifications for C' are given in Section 3.6.2.

## 3.3.3 ASIC/SerDes Test Points (Informative)

ASIC/SerDes transmitter and receiver may be tested on a test board as shown in Figure 4 with nominal trace response as specified by C.1.3 to avoid degradation due to excessive trace loss and to ensure consistent measurements.

FIGURE 4 ASIC/SERDES TEST BOARD

SFI ASIC/SerDes test points are defined as the following:

A SerDes transmitter output at the output of the ASIC/SerDes Test Board. Recommendations for A are given in B.2. D ASIC/SerDes receiver input at the input of the ASIC/SerDes Test Board. Recommendations for D are given in B.3.

## 3.3.4 Host Input Calibration Point

Host receiver input tolerance signals are calibrated through the Host Compliance Board at the output of the Module Compliance Board as shown in Figure 5. The host input calibration point is at C'' with specifications for C'' given in 3.5.2. The response between the connector and C'' is specified by C.1.2.

FIGURE 5 HOST INPUT CALIBRATION POINT C'' AND CROSSTALK SOURCE CALIBRATION POINT B''

## 3.3.5 Module Input Calibration Point

Module transmitter input tolerance signals are calibrated through the Module Compliance Board at the output of the Host Compliance Board as shown in Figure 6. The module input calibration point is at B'' with specifications for B'' given in Section 3.6.1. The response between the connector and B'' is specified by C.1.1.

FIGURE 6 MODULE INPUT CALIBRATION POINT B'' AND CROSSTALK SOURCE CALIBRATION POINT C''

## 3.4 SFI Termination and DC Blocking

The SFI link uses nominal 100 Ohms differential source and load terminations on both the host board and the module. The SFI transmitter provides both differential and common mode termination. The SFI transmitter and receiver termination specifications for each of the compliance points are given by:

## SFP+ 10 Gb/s Electrical Interface

- Host: 3.5 SFP+ Host System Specifications

- Module: 3.6 SFP+ Module Specifications

Host SerDes termination recommendations are given by:

- ASIC/SerDes (Appendix B)

SFP+ modules shall incorporate blocking capacitors or equivalent on all SFI inputs and outputs as shown in Figure 7. The SFI transmitter is represented by terminations Zp and Zn which form a 100 Ohms differential source. Each termination has a nominal value of 50 Ohms, and therefore the common mode impedance is 25 Ohms. The SFI receiver is represented with termination Zdiff with nominal 100 Ohms value. This representation is not intended to preclude the use of other implementations which may provide common mode termination, however the SFI specification does not require any common mode termination at the receiver. If common mode terminations are provided, it may reduce common mode voltage and EMI.

It is recommended that both the module and the host use transmission lines targeted to have 100 Ohms differential impedance with about 7% coupling. SFP+ percent differential coupling is defined by the following equation:

$$Coupling = \frac{Zcm \times 4 - Zdiff}{Zcm \times 4 + Zdiff} \times 100$$

Where Zcm is the common mode impedance and Zdiff is the differential impedance.

Differential traces with nominal 7% coupling offer a good compromise between reasonable common mode match and practical transmission line geometries. These are the targets for the module and host Compliance Boards described in Appendix C.

FIGURE 7 SFI TERMINATION AND AC COUPLING

## 3.5 SFP+ Host System Specifications

SFP+ host system transmitter specifications at compliance point B are given in Section 3.5.1. SFP+ Host system receiver specifications at compliance point C are

## SFP+ 10 Gb/s Electrical Interface

given in Section 3.5.2.

All specifications are to be met at the host compliance test points defined in Section 3.3.1.

The solder pads for the high speed traces in the SFF-8431 Module Compliance Board are 1.1x0.4 mm to improve high frequency performance instead of 2.0x0.5 mm as defined in the SFF-8071 for improved manufacturability. Trade-off between host performance and manufacturability are left to the host designer. For detailed geometry of the Module Compliance Board, see the Gerber files in Section C.3.4.